# Product Technical Specification & Customer Design Guidelines Q64 Wireless CPU<sup>®</sup>

Reference: WA\_DEV\_Q64\_PTS\_001

Revision: 003

Date: January 9, 2009

Wireless CPUs | Operating Systems | Integrated Development Environments | Plug-Ins | Services

# **Q64 Wireless CPU®**

# **Product Technical Specification & Customer Design Guidelines**

Reference: WA\_DEV\_Q64\_PTS\_001 Revision: 003 Date: January 9, 2009

Powered by the Wavecom Open AT® Software Suite

Page: 1 / 116

# **Document History**

| Revision | Date             | List of revisions                                                          |  |

|----------|------------------|----------------------------------------------------------------------------|--|

| 001      | February 6, 2008 | Creation                                                                   |  |

| 002      | July 11, 2008    | Updates                                                                    |  |

| 003      | January 9, 2009  | Updates to sections §3.3.1, §3.15.1, §5.1, §7.13<br>and some minor changes |  |

**Overview**

This document defines and specifies the Q64 Wireless CPU<sup>®</sup>, available in a GSM/GPRS Class 10 quad-band version.

Q64 Wireless CPU<sup>®</sup> is a variant of Wavecom Wireless Microprocessor<sup>®</sup> WMP100, which is pin to pin and functionally compatible with Wavecom Wireless CPU<sup>®</sup> GR64001.

# **Table of Contents**

| Docu                                          | ment History2                                                                                                                                                            | 2     |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Over                                          | <b>view</b> 3                                                                                                                                                            | 6     |

| Table                                         | e of Contents4                                                                                                                                                           | ŀ     |

| Table                                         | e of Figures8                                                                                                                                                            | 5     |

| Trade                                         | emarks                                                                                                                                                                   | )     |

| Сору                                          | right10                                                                                                                                                                  | )     |

| No W                                          | /arranty/No Liability10                                                                                                                                                  | )     |

| 1                                             | References11                                                                                                                                                             |       |

| 1.1<br>1.1<br>1.1                             |                                                                                                                                                                          |       |

| 1.2                                           | List of Abbreviations                                                                                                                                                    | 2     |

| 2                                             | General Description15                                                                                                                                                    | 5     |

| 2.1<br>2.1<br>2.1<br>2.1<br>2.1<br>2.1<br>2.1 | .2       Environment and Mechanics.       15         .3       GSM/GPRS Features       15         .4       Interfaces       16         .5       Operating System       16 | 55555 |

| 2.2<br>2.2                                    | Functional Description                                                                                                                                                   |       |

| 2.3                                           | Operating System                                                                                                                                                         | 3     |

| 2.4                                           | Software Description                                                                                                                                                     | 3     |

| 3                                             | Interfaces20                                                                                                                                                             | )     |

| 3.1                                           | General Interfaces                                                                                                                                                       | )     |

| 3.2                                           | Power Supply                                                                                                                                                             |       |

| 3.2                                           | .1 Power Supply Description                                                                                                                                              | I.    |

####

Page: 4 / 116

| 3.3 Power Consumption                                                                                                                     | 22                         |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| <ul> <li>3.3.1 Power Consumption without Open AT<sup>®</sup> Processing</li></ul>                                                         | 24<br>25<br>27             |

| 3.4 Electrical Information for Digital I/O                                                                                                | 30                         |

| 3.5I2C Bus.3.5.1Features.3.5.2Pin Description.                                                                                            | 32                         |

| <ul> <li>3.6 Main Serial Link (UART1)</li></ul>                                                                                           | 34<br>34                   |

| <ul> <li>3.7 Auxiliary Serial Link (UART2)</li> <li>3.7.1 Features</li> <li>3.7.2 Pin Description</li> <li>3.7.3 Application</li> </ul>   | 39<br>39                   |

| 3.8       SIM Interface         3.8.1       Features         3.8.2       Pin Description         3.8.3       Application                  | 41<br>43                   |

| <ul> <li>3.9 General Purpose Input/Output</li></ul>                                                                                       | 45                         |

| <ul> <li>3.10 Analog to Digital Converter</li> <li>3.10.1 Features</li> <li>3.10.2 Pin Description</li> <li>3.10.3 Application</li> </ul> | 47<br>49                   |

| <ul> <li>3.11 Analogue Audio Interface</li></ul>                                                                                          | 50<br>53<br>55<br>56       |

| <ul> <li>3.12 PWM / Buzzer Output</li></ul>                                                                                               | 67<br>67                   |

| <ul> <li>3.13 Battery Charging Interface</li></ul>                                                                                        | 70<br>71<br>72<br>73<br>73 |

## WƏVECOM<sup>©</sup> © Confidential

Page: 5 / 116

| 5.2<br>5.3               | 5.2 Environmental Specifications |                                                                                     |                |

|--------------------------|----------------------------------|-------------------------------------------------------------------------------------|----------------|

| 5.1                      | Gene                             | eral Purpose Connector Pin-out Description                                          | 99             |

| 5                        | Tec                              | hnical Specifications                                                               | 99             |

| 4.3                      | Tem                              | plate                                                                               | 98             |

| 4.2<br>4.2<br>4.2        | .1                               | ware Configurations<br>Wireless CPU® Configuration<br>Equipment Configuration       | 95             |

| 4.1<br>4.1<br>4.1<br>4.1 | .1<br>.2<br>.3                   | dware Configuration<br>Equipment<br>Wireless CPU® Development Kit<br>SIM cards used | 93<br>95<br>95 |

| 4                        | Con                              | sumption Measurement Procedure                                                      | 93             |

| 3.2<br>3.2               |                                  | nterface<br>RF Connection<br>RF Performances<br>Antenna Specifications              | 91<br>91       |

| 3.2<br>3.2               | USB<br>0.1<br>0.2<br>0.3         | 2.0 Interface<br>Features<br>Pin Description<br>Application                         | 89<br>89       |

| 3.1                      | Digit<br>9.1<br>9.2              | tal Audio Interface (PCM)<br>Features<br>Pin Description                            | 86             |

| 3.1<br>3.1               |                                  | Signal<br>Features<br>Pin Description<br>Application                                | 84<br>85       |

| 3.1<br>3.1               | VRT<br>7.1<br>7.2<br>7.3         | C (Backup Battery)<br>Features<br>Pin Description<br>Application                    | 81<br>82       |

| 3.1<br>3.1               |                                  | F Output<br>Features<br>Pin Description<br>Application                              | 80<br>80       |

| 3.1<br>3.1               |                                  | VICE Signal<br>Features<br>Pin Description<br>Application                           | 79<br>79       |

| 3.1                      | 4.1<br>4.2<br>4.3                | Features<br>Pin Description<br>Application                                          | 74             |

## WƏVECOM<sup>©</sup> © Confidential

Page: 6 / 116

| 5.4<br>5.4<br>5.4               | .1 Physical Characteristics                                                    | 3           |

|---------------------------------|--------------------------------------------------------------------------------|-------------|

| 6                               | Connector Peripheral Devices References10                                      | 5           |

| 6.1                             | General Purpose Connector                                                      |             |

| 6.2                             | SIM Card Reader 10                                                             | 5           |

| 6.3                             | Microphone                                                                     | 5           |

| 6.4                             | Speaker 10                                                                     | 5           |

| 6.5                             | Antenna Adaptor 10                                                             | 6           |

| 6.6                             | Antenna Cable 10                                                               | 6           |

| 6.7                             | GSM Antenna 10                                                                 | 6           |

| 7                               | Noises and Design10                                                            | 7           |

| 7.1<br>7.1<br>7.1<br>7.1<br>7.1 | .2 Power Supply                                                                | 7<br>7<br>8 |

| 7.2                             | Mechanical Integration 10                                                      | 8           |

| 7.3                             | Operating System Upgrade10                                                     | 9           |

| 8                               | Appendix                                                                       | 0           |

| 8.1                             | Standards and Recommendations 11                                               | 0           |

|                                 | Safety Recommendations (For Information Only)11.1RF Safety11.2General Safety11 | 4           |

####

Smart wireless. Smart business.

Product Technical Specification & Customer Design Guidelines

# **Table of Figures**

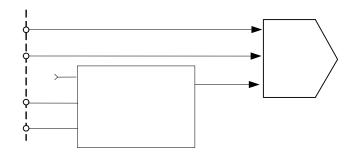

| Figure 1 : Functional architecture17                                              |

|-----------------------------------------------------------------------------------|

| Figure 2: Power supply during burst emission                                      |

| Figure 3: I <sup>2</sup> C Timing diagrams, Master                                |

| Figure 4: I <sup>2</sup> C bus configuration inside the Wireless CPU <sup>®</sup> |

| Figure 5: Example of RS-232 level shifter implementation for UART1                |

| Figure 6: Example of V24/CMOS serial link implementation for UART137              |

| Figure 7: Example of full modem V24/CMOS serial link implementation for UART1     |

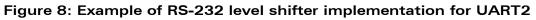

| Figure 8: Example of RS-232 level shifter implementation for UART240              |

| Figure 9: Example of SIM Socket implementation43                                  |

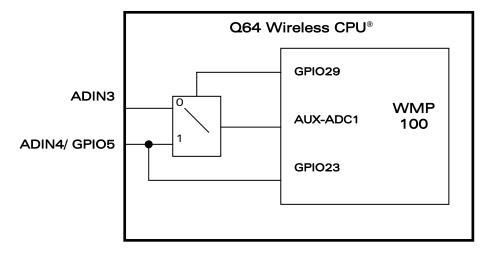

| Figure 10: ADC sharing arrangement48                                              |

| Figure 11: ADIN3 and ADIN4 sharing arrangement48                                  |

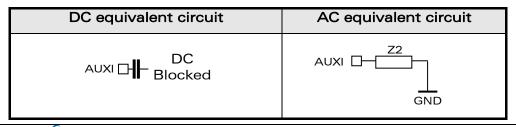

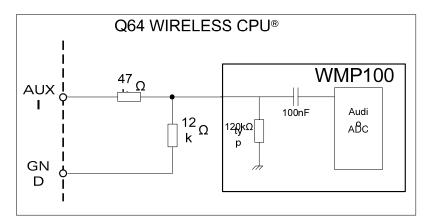

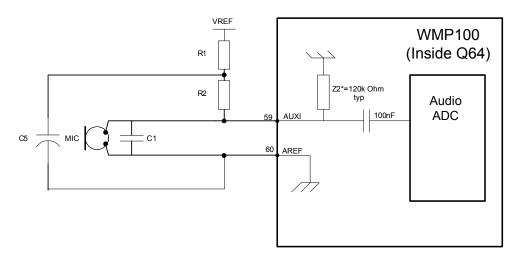

| Figure 12: Auxiliary input connection to Q64 Wireless CPU <sup>®</sup> 52         |

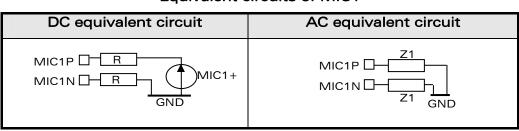

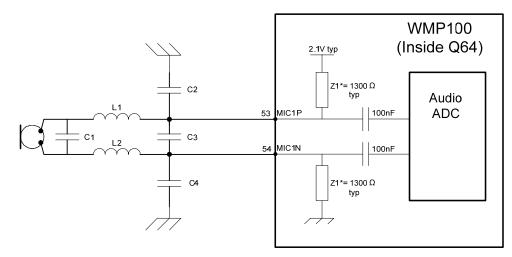

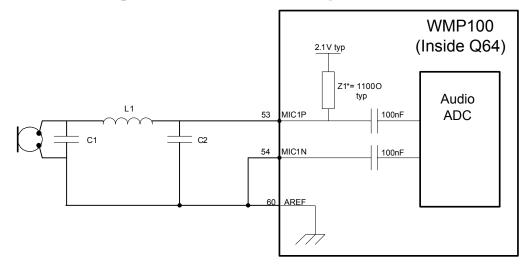

| Figure 13: Example of MIC1 input differential connection with LC filter           |

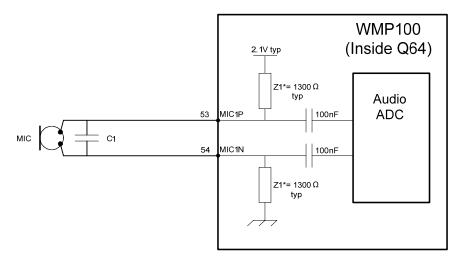

| Figure 14: Example of MIC1 input differential connection without LC filter57      |

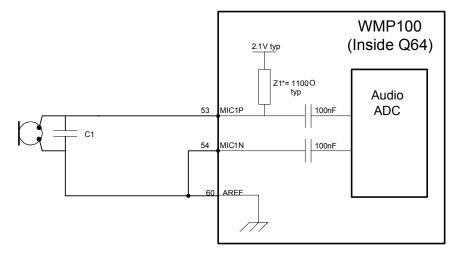

| Figure 15: Example of MIC1 input single-ended connection with LC filter58         |

| Figure 16: Example of MIC1 input single-ended connection without LC filter .58    |

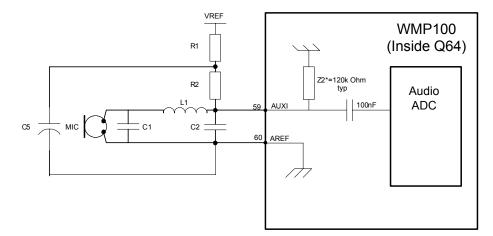

| Figure 17: Example of AUXI input single-ended connection with LC filter59         |

| Figure 18: Example of AUXI input single-ended connection without LC filter60      |

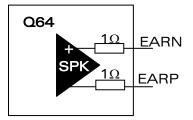

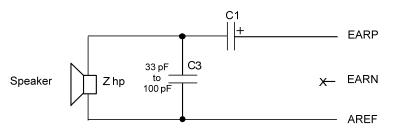

| Figure 19: Example of Speaker differential connection61                           |

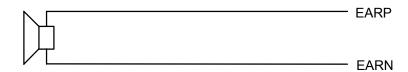

| Figure 20: Example of Earpiece/Speaker single-ended connection61                  |

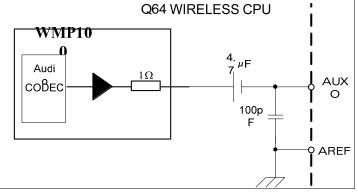

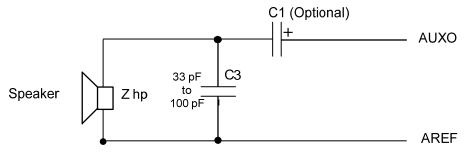

| Figure 21: Example of AUXO connection62                                           |

| Figure 22: Microphone63                                                           |

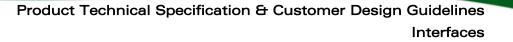

| Figure 23: Audio track design                                                     |

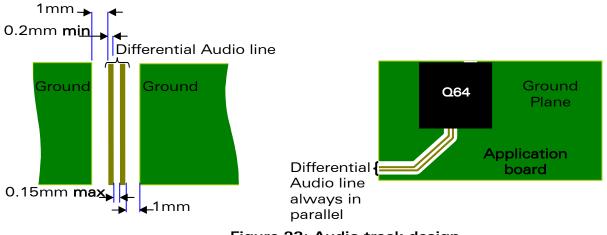

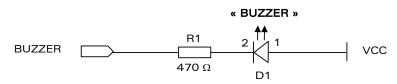

| Figure 24: Example of buzzer implementation68                                     |

| Figure 25: Example of LED driven by the BUZZER output69                           |

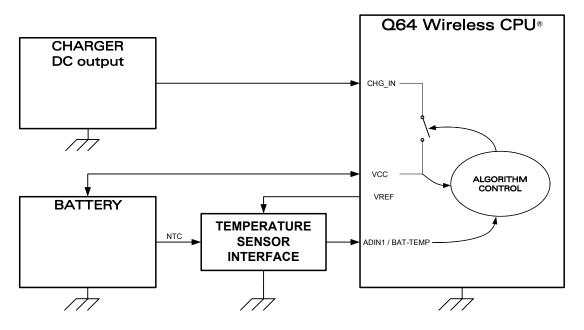

| Figure 26: Charging block diagram70                                               |

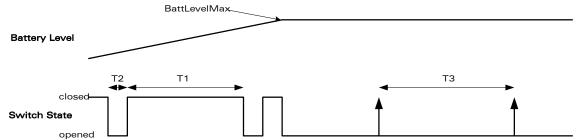

| Figure 27: Ni-Cd / Ni-Mh charging waveform71                                      |

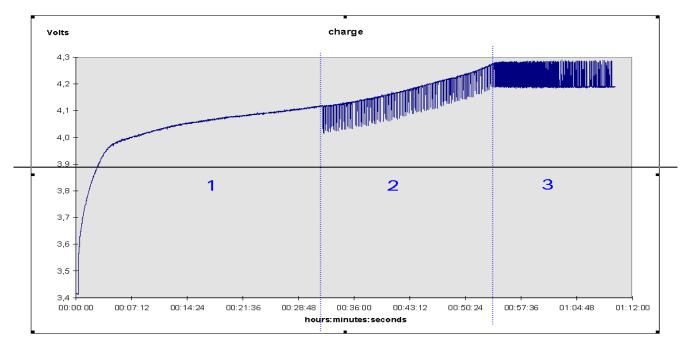

| Figure 28: Li-Ion full-charging waveform72                                        |

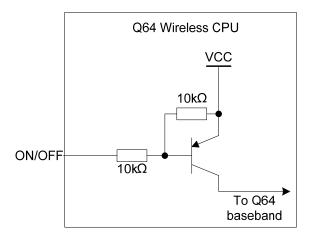

| Figure 29: ON/OFF circuitry inside Q6475                                          |

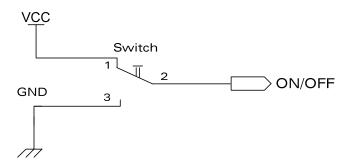

| Figure 30: Example of ON/OFF pin connection75                                     |

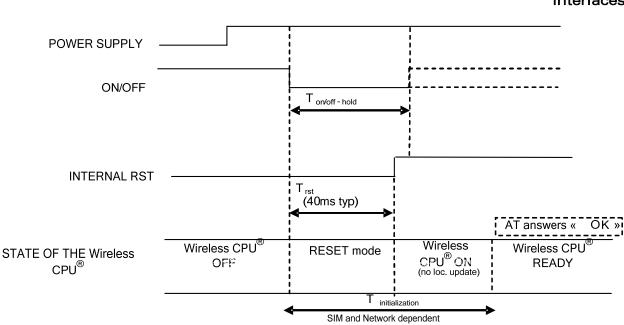

| Figure 31 : Power-ON sequence (no PIN code activated)76                           |

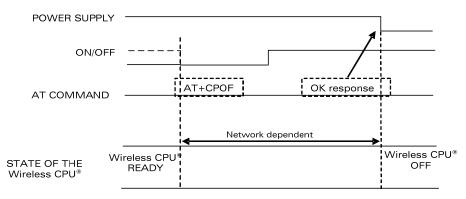

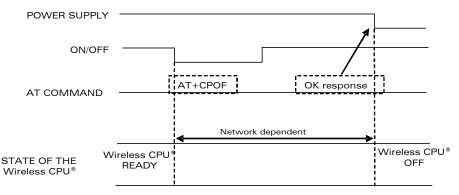

| Figure 32: Power-OFF sequence without GR plug-in in Q6478                         |

| Figure 33: Power-OFF sequence with GR plug-in in Q6478                            |

####

Page: 8 / 116

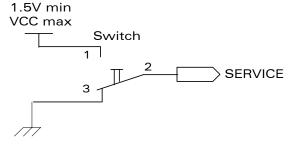

| Figure 34: Example of SERVICE pin implementation           | 80  |

|------------------------------------------------------------|-----|

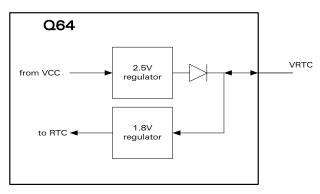

| Figure 35 : Real Time Clock power supply                   | 81  |

| Figure 36: RTC supplied by a gold capacitor                | 82  |

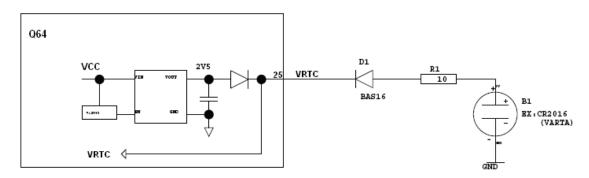

| Figure 37: RTC supplied by a non rechargeable battery      | 83  |

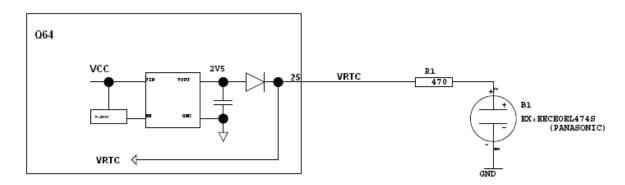

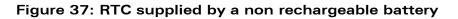

| Figure 38: RTC supplied by a rechargeable battery cell     | 83  |

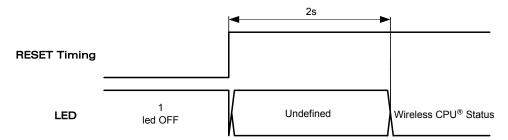

| Figure 39 : LED state during RESET and Initialization time | 85  |

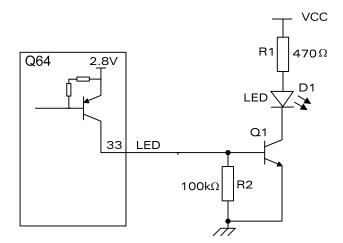

| Figure 40: Example of GSM activity status implementation   | 85  |

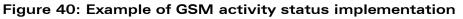

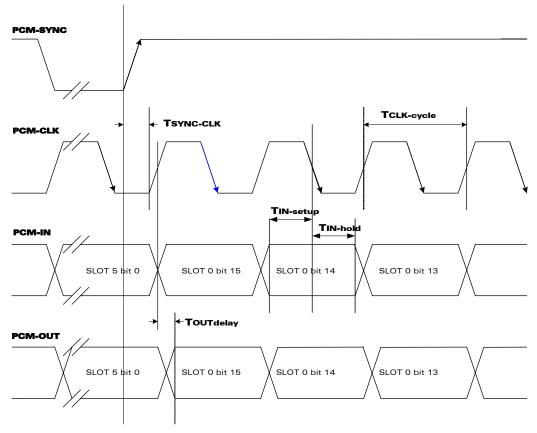

| Figure 41 : PCM Frame waveform                             | 87  |

| Figure 42 : PCM Sampling waveform                          | 88  |

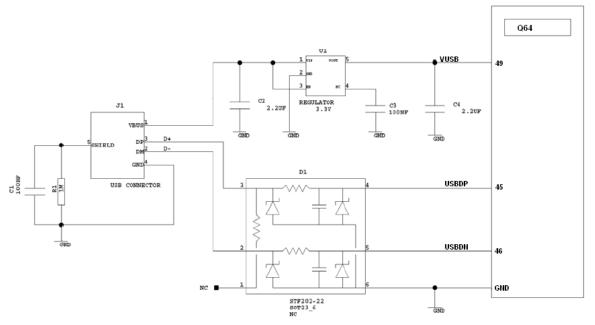

| Figure 43: Example of USB implementation                   | 90  |

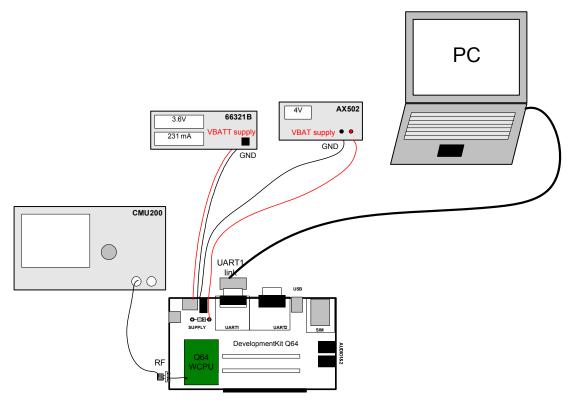

| Figure 44: Typical hardware configuration                  | 94  |

| Figure 45 : Environmental classes                          | 102 |

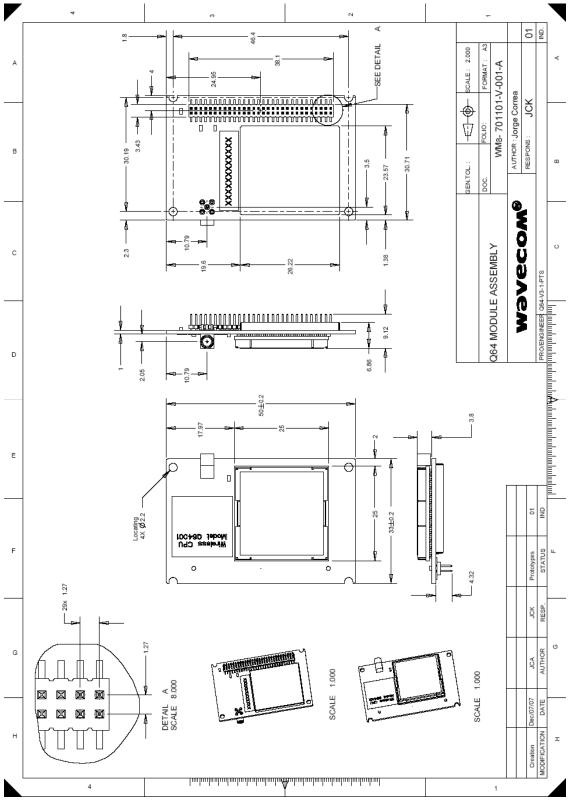

| Figure 46 : Mechanical drawing                             | 104 |

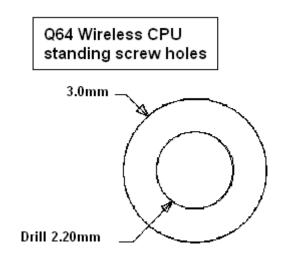

| Figure 47: Standing screw holes requirement                | 108 |

# **Trademarks**

OPEN AT

**Wavecon**<sup>®</sup>, **Wireless** Microprocessor<sup>®</sup>, Wireless CPU<sup>®</sup>, Open AT<sup>®</sup> and certain other trademarks and logos appearing on this document, are filed or registered trademarks of Wavecom S.A. in France and/or in other countries. All other company and/or product names mentioned may be filed or registered trademarks of their respective owners.

# Copyright

This manual is copyrighted by WAVECOM with all rights reserved. No part of this manual may be reproduced, modified or disclosed to third parties in any form without the prior written permission of WAVECOM.

# **No Warranty/No Liability**

This document is provided "as is". Wavecom makes no warranties of any kind, either expressed or implied, including any implied warranties of merchantability, fitness for a particular purpose, or noninfringement. The recipient of the documentation shall endorse all risks arising from its use. In no event shall Wavecom be liable for any incidental, direct, indirect, consequential, or punitive damages arising from the use or inadequacy of the documentation, even if Wavecom has been advised of the possibility of such damages and to the extent permitted by law.

####

# **1 References**

# **1.1 Reference Documents**

For more details, several documents are referenced in this specification. The Wavecom documents references herein are provided in the Wavecom documentation package; the general reference documents which are not Wavecom owned are not provided in the documentation package.

## **1.1.1 Wavecom Reference Documentation**

- Wireless Microprocessor<sup>®</sup> WMP100 Technical Specification (Ref: WM\_DEV\_WUP\_PTS\_004)

- Wireless CPU<sup>®</sup> Q64 Hardware Differences between Q64 and GR64 (Ref: WA\_DEV\_Q64\_PTS\_002)

- [3] Integrator's Manual GR64 GSM/GPRS Wireless CPU<sup>®</sup> (Ref: WI\_DEV\_GR64\_UGD\_001)

- [4] AT Command Interface Guide for Open AT<sup>®</sup> Firmware v6.5 (Ref: WM\_DEV\_OAT\_UGD\_035)

- [5] Q64 software user guide (Ref: WA\_DEV\_Q64\_UGD\_003)

- [6] AT Command Manual for GR64 and GS64 Wireless CPU<sup>®</sup> (Ref: WI\_DEV\_ Gx64\_UGD\_001)

#### **1.1.2 General Reference Documentation**

- [7] "I<sup>2</sup>C Bus Specification", Version 2.0, Philips Semiconductor 1998

- [8] ISO 7816-3 Standard

# **1.2 List of Abbreviations**

# **Abbreviation Definition**

| AC    | Alternative Current                     |  |  |

|-------|-----------------------------------------|--|--|

| ADC   | Analog to Digital Converter             |  |  |

| A/D   | Analog to Digital conversion            |  |  |

| AF    | Audio-Frequency                         |  |  |

| AT    | ATtention (prefix for modem commands)   |  |  |

| AUX   | AUXiliary                               |  |  |

| CAN   | Controller Area Network                 |  |  |

| СВ    | Cell Broadcast                          |  |  |

| CEP   | Circular Error Probable                 |  |  |

| CLK   | CLocK                                   |  |  |

| CMOS  | Complementary Metal Oxide Semiconductor |  |  |

| CS    | Coding Scheme                           |  |  |

| CTS   | Clear To Send                           |  |  |

| DAC   | Digital to Analogue Converter           |  |  |

| dB    | Decibel                                 |  |  |

| DC    | Direct Current                          |  |  |

| DCD   | Data Carrier Detect                     |  |  |

| DCE   | Data Communication Equipment            |  |  |

| DCS   | Digital Cellular System                 |  |  |

| DR    | Dynamic Range                           |  |  |

| DSR   | Data Set Ready                          |  |  |

| DTE   | Data Terminal Equipment                 |  |  |

| DTR   | Data Terminal Ready                     |  |  |

| EFR   | Enhanced Full Rate                      |  |  |

| E-GSM | Extended GSM                            |  |  |

| EMC   | ElectroMagnetic Compatibility           |  |  |

| EMI   | ElectroMagnetic Interference            |  |  |

| EMS   | Enhanced Message Service                |  |  |

| EN    | ENable                                  |  |  |

| ESD   | ElectroStatic Discharges                |  |  |

| FIFO  | First In Fi <b>rst O</b> ut             |  |  |

|       |                                         |  |  |

####

Page: 12 / 116

Product Technical Specification & Customer Design Guidelines References

| Abbreviation | Definition                                               |

|--------------|----------------------------------------------------------|

| FR           | Full Rate                                                |

| FTA          | Full Type Approval                                       |

| GND          | GrouND                                                   |

| GPI          | General Purpose Input                                    |

| GPC          | General Purpose Connector                                |

| GPIO         | General Purpose Input Output                             |

| GPO          | General Purpose Output                                   |

| GPRS         | General Packet Radio Service                             |

| GPS          | Global Positioning System                                |

| GSM          | Global System for Mobile communications                  |

| HR           | Half Rate                                                |

| I/O          | Input / <b>O</b> utput                                   |

| LED          | Light Emitting Diode                                     |

| LNA          | Low Noise Amplifier                                      |

| MAX          | MAXimum                                                  |

| MIC          | MICrophone                                               |

| MIN          | MINimum                                                  |

| MMS          | Multimedia Message Service                               |

| MO           | Mobile Originated                                        |

| МТ           | Mobile Terminated                                        |

| na           | Not Applicable                                           |

| NF           | Noise Factor                                             |

| NMEA         | National Marine Electronics Association                  |

| NOM          | NOMinal                                                  |

| NTC          | Négative Temperature Coefficient                         |

| PA           | Power Amplifier                                          |

| Pa           | <b>Pa</b> scal (for speaker sound pressure measurements) |

| PBCCH        | Packet Broadcast Control CHannel                         |

| PC           | Personal Computer                                        |

| PCB          | Printed Circuit Board                                    |

| PDA          | Personal Digital Assistant                               |

| PFM          | Power Frequency Modulation                               |

| PSM          | Phase Shift Modulation                                   |

| PWM          | Pulse Width Modulation                                   |

####

Page: 13 / 116

| Definition                                       |  |  |

|--------------------------------------------------|--|--|

| Random Access Memory                             |  |  |

| Radio Frequency                                  |  |  |

| Radio Frequency Interference                     |  |  |

| Right Hand Circular Polarization                 |  |  |

| Ring Indicator                                   |  |  |

| ReSeT                                            |  |  |

| Real Time Clock                                  |  |  |

| Radio Technical Commission for Maritime services |  |  |

| Request To Send                                  |  |  |

| Receive                                          |  |  |

| Serial CLock                                     |  |  |

| Serial DAta                                      |  |  |

| Subscriber Identification Module                 |  |  |

| Short Message Service                            |  |  |

| Serial Peripheral Interface                      |  |  |

| Sound Pressure Level                             |  |  |

| SPeaKer                                          |  |  |

| Pseudo Static RAM                                |  |  |

| To Be Confirmed                                  |  |  |

| Time Division Multiple Access                    |  |  |

| Test Point                                       |  |  |

| Transient Voltage Suppressor                     |  |  |

| Transmit                                         |  |  |

| TYPical                                          |  |  |

| Universal Asynchronous Receiver-Transmitter      |  |  |

| Universal Serial Bus                             |  |  |

| Unstructured Supplementary Services Data         |  |  |

| Voltage Standing Wave Ratio                      |  |  |

|                                                  |  |  |

####

# **2** General Description

# **2.1 General Information**

The Q64 Wireless CPU<sup>®</sup> is a self-contained E-GSM/GPRS 900/1800 and 850/1900 quad-band Wireless CPU<sup>®</sup>, including the characteristics listed in the subsection below:

# 2.1.1 Overall Dimensions

- Length: 50 mm

- Width: 33 mm

- Thickness: 6.9 mm

- Weight: 11.6 g

# 2.1.2 Environment and Mechanics

- Green policy: Restriction of Hazardous Substances in Electrical and Electronic Equipment (RoHS) compliant

- Complete shielding

The Q64 Wireless CPU<sup>®</sup> is compliant with RoHS Directive 2002/95/EC, which sets limits for the use of certain restricted hazardous substances. This directive states that "from 1st July 2006, new electrical and electronic equipment sold on the market does not contain lead, mercury, cadmium, hexavalent chromium, polybrominated biphenyls (PBB), and polybrominated diphenyl ethers (PBDE)".

# 2.1.3 GSM/GPRS Features

- 2-Watt EGSM 900/GSM 850 radio section running under 3.6 volts

- 1-Watt GSM1800/1900 radio section running under 3.6 volts

- Hardware GPRS class 10 capable

####

Page: 15 / 116

#### 2.1.4 Interfaces

- Digital section running under 2.8 volts

- 3V/1V8 SIM interface

- Power supply

- Serial links (UART)

- Analogue audio

- ADC

- PCM digital audio

- USB 2.0 slave

- I2C Serial buses

- PWM (BUZZER)

- GPIOs

#### 2.1.5 Operating System

- Real Time Clock (RTC) with calendar

- Echo Cancellation + noise reduction (quadri codec)

- Full GSM or GSM/GPRS Operating System stack

#### 2.1.6 Connection Interfaces

The Q64 Wireless CPU® has two external connections:

- One for RF circuit:

- MMCX connector

- One for baseband signals:

- o 60-pin I/O connector

#

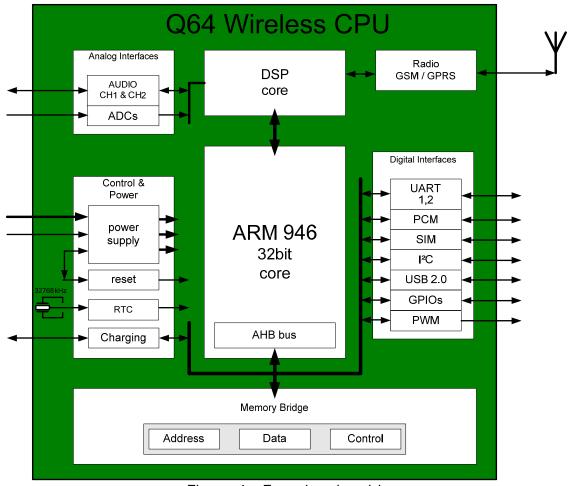

# **2.2 Functional Description**

The global architecture of Q64 Wireless CPU<sup>®</sup> is described below:

Figure 1 : Functional architecture

#

Page: 17 / 116

#### 2.2.1 **RF Functionalities**

The Radio Frequency (RF) range complies with the Phase II EGSM 900/DCS 1800 and GSM 850/PCS 1900 recommendation. The frequencies are listed in the table below:

|                                 | Transmit band (Tx) | Receive band (Rx) |

|---------------------------------|--------------------|-------------------|

| <b>GSM 850</b> 824 to 849 MHz 8 |                    | 869 to 894 MHz    |

| E-GSM 900                       | 880 to 915 MHz     | 925 to 960 MHz    |

| DCS 1800                        | 1710 to 1785 MHz   | 1805 to 1880 MHz  |

| PCS 1900                        | 1850 to 1910 MHz   | 1930 to 1990 MHz  |

The Q64 Wireless CPU<sup>®</sup> is designed to be used with Wavecom WMP100 Wireless Microprocessor<sup>®</sup>. The Radio Frequency (RF) part is based on a specific quad-band chip with a:

- Digital low-IF receiver

- Quad-band LNA (Low Noise Amplifier)

- Offset PLL (Phase Locked Loop) transmitter

- Frequency synthesizer

- Digitally controlled crystal oscillator (DCXO)

- Tx/Rx FEM (Front-End Module) for quad-band GSM/GPRS

# **2.3 Operating System**

The Q64 Wireless CPU<sup>®</sup> is designed to integrate various types of specific process applications such as telemetry, multimedia, automotive known as vertical applications.

The Operating System provides a set of AT commands to control the Wireless CPU<sup>®</sup>. With this standard Operating System, some interfaces of the Wireless CPU<sup>®</sup> are not available, since they are dependent on the peripheral devices connected to the Wireless CPU<sup>®</sup>.

The Operating System is Open AT<sup>®</sup> compliant.

# **2.4 Software Description**

The software package of Q64, Open AT<sup>®</sup> Software Suite v1.0 / v2.0, includes:

- An Open AT<sup>®</sup> Firmware v6.5 which drives the Q64 and offer an AT command interface over a serial port or USB.

- An Open AT<sup>®</sup> Operating System (OS) v5.0 which runs various types of applications (telemetry, multimedia, automotive...)

- An Open AT<sup>®</sup> Integrated Development Environment (IDE) which builds and debugs applications over the Open AT<sup>®</sup> Operating System

####

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged without prior written agreement.

- Several other Open AT<sup>®</sup> plug-in softwares are able to run over the Open AT<sup>®</sup> Operating System.

- A "GR plug-in" software that provides software compatibility with GR64 Wireless CPU<sup>®</sup>, in terms of AT commands and system operation. It is specifically designed for GR64 Wireless CPU<sup>®</sup> compatibility.

# **3** Interfaces

# **3.1 General Interfaces**

Every hardware interface of the Q64 can be accessed with the Q64 development kit, or GR64 Tina or UMA Board.

| Chapter | Name                          | Driven by AT commands | Driven by Open AT® |

|---------|-------------------------------|-----------------------|--------------------|

| 3.6     | Main Serial Link              | х                     | х                  |

| 3.7     | Auxiliary Serial Link         | х                     | х                  |

| 3.8     | SIM Interface                 | х                     | х                  |

| 3.9     | General Purpose IO            | х                     | х                  |

| 3.5     | Serial Interface (I2C Bus)    |                       | х                  |

| 3.10    | Analog to Digital Converter   | х                     | х                  |

| 3.12    | PWM / Buzzer Output           | х                     | х                  |

| 3.13    | Battery charging interface    | Х                     | х                  |

| 3.17    | VRTC (Backup Battery)         | Х                     | х                  |

| 3.18    | LED signal                    | Х                     | Х                  |

| 3.19    | Digital Audio Interface (PCM) | Х                     | х                  |

| 3.20    | USB 2.0 Interface             | Х                     | х                  |

The available interfaces are described in the table below:

####

Interfaces

# 3.2 Power Supply

# 3.2.1 **Power Supply Description**

The power supply is one of the key issues in the design of a GSM terminal.

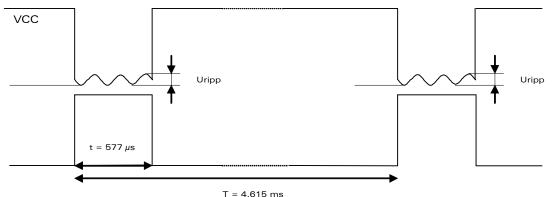

Due to the burst emission mode used in GSM/GPRS, the power supply should deliver high current peaks in a short time. During the peaks, the ripple ( $U_{ripp}$ ) on the supply voltage must not exceed a certain limit (see Table 1 Power supply voltage "Power Supply Voltage").

• In communication mode, a GSM/GPRS class 2 terminal emits 577μs radio bursts every 4.615ms (see Figure 2 below).

Figure 2: Power supply during burst emission

- In communication mode, a GPRS class 10 terminal emits 1154  $\mu s$  radio bursts every 4.615 ms.

The VCC power supply input is only available for Q64 Wireless CPU<sup>®</sup>.

VCC:

• Directly supplies the RF components with 3.6 V. It is essential to keep a minimum voltage ripple at this connection in order to avoid any phase error.

The RF Power Amplifier current (1.5 A peak in GSM /GPRS mode) flows with a ratio of:

- $\circ$  1/8 of the time (around 577  $\mu$ s every 4.615 ms for GSM /GPRS cl. 2) and

- $\circ~$  2/8 of the time (around 1154  $\mu s$  every 4.615 ms for GSM /GPRS cl. 10).

The rising time is around  $10\mu s$ .

• Is internally used to provide, via several regulators, the supply required for the baseband signals.

####

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged without prior written agreement.

# **3.2.2 Electrical Characteristics**

#### Input power supply voltage

|                    | V <sub>MIN</sub> | V <sub>NOM</sub> | V <sub>MAX</sub> | I <sub>MAX</sub> | Ripple max (U <sub>ripp</sub> ) |

|--------------------|------------------|------------------|------------------|------------------|---------------------------------|

| VCC <sup>1,2</sup> | 3.2              | 3.6              | 4.8              | 1.8 A            | 10mV                            |

Table 1 Power supply voltage

(1): This value must be guaranteed during the burst (with 1.5A Peak in GSM or GPRS mode)(2): Maximum operating Voltage Stationary Wave Ratio (VSWR) 2:1

When powering the WMP100 with a battery, the total impedance (battery + protections + PCB) should be <150 m $\Omega$ .

# 3.2.3 Power Supply Pin-out

## Power supply pin-out

| Signal | Pin number    |

|--------|---------------|

| VCC    | 1,3,5,7,9     |

| GND    | 2,4,6,8,10,12 |

# WƏVECOM<sup>©</sup> © Confidential

# **3.3 Power Consumption**

Power consumption depends on the configuration. Therefore, the following consumption values are given for each mode, RF band and type of software used (with or without an Open AT<sup>®</sup> application).

Note: The following information is provided assuming a 50  $\Omega$  RF output.

The following consumption values were obtained by performing measurements on Q64 samples at a temperature of 25° C.

Three VCC values are used to measure the consumption, VCC<sub>MIN</sub> (3.2V), VCC<sub>MAX</sub> (4.8V) and VCC<sub>TYP</sub> (3.6V).

The average current is given for the three VCC values and the peak current given is the maximum current peak measured with the three VCC voltages.

For more detailed descriptions of the operating modes, (refer to the document [4] AT Command Interface Guide for Open AT<sup>®</sup> Firmware v6.5).

For more information about the consumption measurement procedure, refer to section 4.

####

## 3.3.1 Power Consumption without Open AT<sup>®</sup> Processing

The following measurements are relevant when no processing is required by the Open AT<sup>®</sup> application:

Either there is no Open AT<sup>®</sup> application or the Open AT<sup>®</sup> application is disabled

|           |                              | Power c          | onsumption without C      | pen AT <sup>®</sup> a                     | pplication                                |                                           |                          |      |

|-----------|------------------------------|------------------|---------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|--------------------------|------|

| Operati   | ng mode                      | Parameters       |                           | I <sub>MIN</sub><br>average<br>VBATT=4,8V | I <sub>№ОМ</sub><br>average<br>VBATT=3,6V | I <sub>MAX</sub><br>average<br>VBATT=3,2V | I <sub>MAX</sub><br>peak | unit |

| Alarm M   | lode                         |                  | 27                        | 19                                        | 17                                        | N/A                                       | μA                       |      |

| Fast Idl  | e Mode                       | Paging 9 (Rx bu  | rst occurrence ~2s)       | 16.4                                      | 17.6                                      | 18.5                                      | 160 <sub>RX</sub>        | mA   |

| i uot iui | 0 111000                     | Paging 2 (Rx bui | rst occurrence ~0,5s)     | 17.8                                      | 19.2                                      | 20.1                                      | 160 <sub>RX</sub>        | mA   |

| Slow Id   | le Mode <sup>1</sup>         | Paging 9 (Rx bu  | rst occurrence ~2s)       | 2.7                                       | 2.6                                       | 2.6                                       | 160 <sub>RX</sub>        | mA   |

|           |                              | Paging 2 (Rx bur | rst occurrence ~0,5s)     | 5.3                                       | 5.4                                       | 5.6                                       | 160 <sub>RX</sub>        | mA   |

| Fast Sta  | andby Mode                   | ·                |                           | 32.1                                      | 38.1                                      | 42.4                                      | 80                       | mA   |

| Slow St   | andby Mode                   |                  |                           | 2.1                                       | 1.9                                       | 1.8                                       | 80                       | mA   |

|           |                              | 850/900 MHz      | PCL5 (TX power 33dBm)     | 206/206                                   | 215/214                                   | 221/219                                   | 1500 <sub>TX</sub>       | mA   |

| Connoc    | ted Mode                     | 830/900 Miliz    | PCL19 (TX power 5dBm)     | 83/84                                     | 91/91                                     | 95/95                                     | 270 <sub>TX</sub>        | mA   |

| Connec    |                              | 1800/1900 MHz    | PCL0 (TX power 30dBm)     | 147/154                                   | 156/164                                   | 160/169                                   | 900 <sub>TX</sub>        | mA   |

|           |                              | 1000/1000 10112  | PCL15 (TX power 0dBm)     | 80/80                                     | 87/88                                     | 91/92                                     | 250 <sub>TX</sub>        | mA   |

|           |                              | 850/900 MHz      | Gam.3 (TX power<br>33dBm) | 197/197                                   | 206/205                                   | 211/210                                   | 1500 <sub>TX</sub>       | mA   |

|           | Transfer<br>Mode             | 650/900 MIHZ     | Gam.17 (TX power<br>5dBm) | 79/80                                     | 86/87                                     | 90/91                                     | 270 <sub>TX</sub>        | mA   |

|           | class 8<br>(4Rx/1Tx)         | 1800/1900 MHz    | Gam.3 (TX power<br>30dBm) | 141/147                                   | 149/157                                   | 153/162                                   | 900 <sub>TX</sub>        | mA   |

| GPRS      |                              |                  | Gam.18 (TX power<br>0dBm) | 76/76                                     | 83/83                                     | 87/87                                     | 250 <sub>TX</sub>        | mA   |

| or no     |                              | 850/900 MHz      | Gam.3 (TX power<br>33dBm) | 354/353                                   | 365/362                                   | 372/370                                   | 1500 <sub>TX</sub>       | mA   |

|           | Transfer<br>Mode<br>class 10 |                  | Gam.17 (TX power<br>5dBm) | 121/114                                   | 116/122                                   | 125/126                                   | 270 <sub>TX</sub>        | mA   |

|           | (3Rx/2Tx)                    | 1800/1900 MHz    | Gam.3 (TX power<br>30dBm) | 238/250                                   | 248/264                                   | 253/271                                   | 900 <sub>TX</sub>        | mA   |

|           |                              |                  | Gam.18 (TX power<br>0dBm) | 106/107                                   | 114/115                                   | 118/119                                   | 250 <sub>TX</sub>        | mA   |

TX means that the current peak is the RF transmission burst (Tx burst)

<sub>RX</sub> means that the current peak is the RF reception burst (Rx burst)

<sup>1</sup>**Fast Idle Mode** the signal of DTR1 (pin 37) is at high level.

<sup>2</sup>Slow Idle Mode consumption depends on the SIM card used. Some SIM cards respond faster than others; The longer the response time is, the higher the consumption is.

####

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged without prior written agreement.

WA\_DEV\_Q64\_PTS\_001-003

Interfaces

#### **3.3.2** Power Consumption with a Dhrystone Open AT<sup>®</sup> Application

The Open AT<sup>®</sup> application used is the Dhrystone application. The following consumption results are measured during the Dhrystone application run. The two tables are respectively for the CPU clock programmed at 26MHz and 104MHz.

| Power             | Power consumption with Dhrystone Open AT® application@26MHz |                 |                        |                                               |                                               |                                               |                          |      |  |  |

|-------------------|-------------------------------------------------------------|-----------------|------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|--------------------------|------|--|--|

| Operati           | ng mode                                                     | Parameters      |                        | I <sub>MIN</sub><br>average<br>VBATT=4,8<br>V | I <sub>NOM</sub><br>average<br>VBATT=3,6<br>V | I <sub>MAX</sub><br>average<br>VBATT=3,2<br>V | I <sub>MAX</sub><br>peak | unit |  |  |

| Alarm N           | lode                                                        |                 | N/A                    | N/A                                           | N/A                                           | N/A                                           |                          |      |  |  |

| Fast Idl          | e Mode                                                      | Paging 9 (Rx bu | rst occurrence ~2s)    | 33                                            | 40                                            | 42                                            | 180 <sub>RX</sub>        | mA   |  |  |

| i dot idi         |                                                             | Paging 2 (Rx bu | rst occurrence ~0,5s)  | 34                                            | 39                                            | 43                                            | 180 <sub>RX</sub>        | mA   |  |  |

| Slow Id           | le Mode <sup>1</sup>                                        | Paging 9 (Rx bu | rst occurrence ~2s)    | N/A                                           | N/A                                           | N/A                                           | N/A                      |      |  |  |

|                   |                                                             |                 | rst occurrence ~0,5s)  | N/A                                           | N/A                                           | N/A                                           | N/A                      |      |  |  |

| Fast Sta          | andby Mode                                                  | l               | 33                     | 39                                            | 43                                            | 60                                            | mA                       |      |  |  |

| Slow Standby Mode |                                                             |                 |                        | N/A                                           | N/A                                           | N/A                                           | N/A                      |      |  |  |

|                   |                                                             | 850/900 MHz     | PCL5 (TX power 33dBm)  | 202 / 208                                     | 214 / 218                                     | 219 / 224                                     | 1440 <sub>TX</sub>       | mA   |  |  |

| Connec            | ted Mode                                                    | 000/000 10112   | PCL19 (TX power 5dBm)  | 84 / 84                                       | 92 / 92                                       | 96 / 96                                       | 270 <sub>TX</sub>        | mA   |  |  |

| Connec            |                                                             | 1800/1900 MHz   | PCL0 (TX power 30dBm)  | 148 / 161                                     | 157 / 164                                     | 161 / 170                                     | 260 <sub>TX</sub>        | mA   |  |  |

|                   |                                                             | 1000/1000 10112 | PCL15 (TX power 0dBm)  | 80 / 81                                       | 88 / 89                                       | 92 / 93                                       | 230 <sub>TX</sub>        | mA   |  |  |

|                   | Transfer                                                    | 850/900 MHz     | Gam.3 (TX power 33dBm) | 195 / 181                                     | 195 / 208                                     | 215 / 214                                     | 1420 <sub>TX</sub>       | mA   |  |  |

|                   | Mode<br>class 8                                             | 000/000 1112    | Gam.17 (TX power 5dBm) | 80 / 80                                       | 87 / 88                                       | 91 / 92                                       | 240 <sub>TX</sub>        | mA   |  |  |

|                   | (4Rx/1Tx)                                                   | 1800/1900 MHz   | Gam.3 (TX power 30dBm) | 141 / 148                                     | 150 / 157                                     | 154 / 163                                     | 930 <sub>TX</sub>        | mA   |  |  |

| GPRS              | (41\\/11\)                                                  |                 | Gam.18 (TX power 0dBm) | 76 / 77                                       | 84 / 84                                       | 87 / 88                                       | 210 <sub>TX</sub>        | mA   |  |  |

| 5                 | Transfer                                                    | 850/900 MHz     | Gam.3 (TX power 33dBm) | 350 / 358                                     | 361 / 369                                     | 368 / 378                                     | 1460 <sub>TX</sub>       | mA   |  |  |

|                   | Mode<br>class 10                                            |                 | Gam.17 (TX power 5dBm) | 116 / 115                                     | 119 / 123                                     | 126 / 127                                     | 270 <sub>TX</sub>        | mA   |  |  |

|                   | (3Rx/2Tx)                                                   | 1800/1900 MHz   | Gam.3 (TX power 30dBm) | 239 / 251                                     | 249 / 264                                     | 254 / 271                                     | 960 <sub>TX</sub>        | mA   |  |  |

|                   |                                                             |                 | Gam.18 (TX power 0dBm) | 106 / 109                                     | 115 / 116                                     | 119 / 120                                     | 260 <sub>TX</sub>        | mA   |  |  |

$_{\mathsf{TX}}$  means that the current peak is the RF transmission burst (Tx burst)

<sub>RX</sub> means that the current peak is the RF reception burst (Rx burst)

\*N/A: It does not mean that no Open AT<sup>®</sup> application is possible in this specific mode. That means that the specific Dhrystone Open AT<sup>®</sup> application cannot allow this specific mode. (This is a worst case for the consumption measurement)

#

|                   |                  | Power consum          | ption with Dhrystone Op | oen AT <sup>®</sup> application@104MHz        |                                               |                                               |                          |      |  |

|-------------------|------------------|-----------------------|-------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|--------------------------|------|--|

| Operati           | ng mode          | Parameters            |                         | I <sub>MIN</sub><br>average<br>VBATT=4,8<br>V | I <sub>NOM</sub><br>average<br>VBATT=3,6<br>V | I <sub>MAX</sub><br>average<br>VBATT=3,2<br>V | I <sub>MAX</sub><br>peak | unit |  |

| Alarm Mode        |                  |                       |                         | N/A                                           | N/A                                           | N/A                                           | N/A                      |      |  |

| Fast Idl          | e Mode           | Paging 9 (Rx bu       | rst occurrence ~2s)     | 73                                            | 89                                            | 96                                            | 240 <sub>RX</sub>        | mA   |  |

| i uot iui         |                  | Paging 2 (Rx but      | rst occurrence ~0,5s)   | 72                                            | 88                                            | 96                                            | 240 <sub>RX</sub>        | mA   |  |

| Slow Idle Mode'   |                  | rst occurrence ~2s)   | N/A                     | N/A                                           | N/A                                           | N/A                                           |                          |      |  |

|                   |                  | rst occurrence ~0,5s) | N/A                     | N/A                                           | N/A                                           | N/A                                           |                          |      |  |

| Fast Standby Mode |                  |                       |                         | 63                                            | 80                                            | 86                                            | 110                      | mA   |  |

| Slow Standby Mode |                  |                       |                         | N/A                                           | N/A                                           | N/A                                           | N/A                      |      |  |

|                   |                  | 850/900 MHz           | PCL5 (TX power 33dBm)   | 233 / 236                                     | 252 / 256                                     | 262 / 267                                     | 1550 <sub>TX</sub>       | mA   |  |

| Connec            | ted Mode         | 000/000 10112         | PCL19 (TX power 5dBm)   | 112 / 113                                     | 130 / 130                                     | 139 / 140                                     | 320 <sub>TX</sub>        | mA   |  |

| oonnee            |                  | 1800/1900 MHz         | PCL0 (TX power 30dBm)   | 176 / 183                                     | 195 / 202                                     | 205 / 209                                     | 990 <sub>TX</sub>        | mA   |  |

|                   |                  | 1000/1000 1012        | PCL15 (TX power 0dBm)   | 109 / 109                                     | 126 / 127                                     | 135 / 136                                     | 280 <sub>TX</sub>        | mA   |  |

|                   | Transfer         | 850/900 MHz           | Gam.3 (TX power 33dBm)  | 223 / 227                                     | 241 / 245                                     | 251 / 253                                     | 1540 <sub>ТХ</sub>       | mA   |  |

|                   | Mode<br>class 8  |                       | Gam.17 (TX power 5dBm)  | 108 / 108                                     | 124 / 125                                     | 133 / 134                                     | 290 <sub>TX</sub>        | mA   |  |

|                   | (4Rx/1Tx)        | 1800/1900 MHz         | Gam.3 (TX power 30dBm)  | 169 / 175                                     | 187 / 194                                     | 196 / 204                                     | 260 <sub>TX</sub>        | mA   |  |

| GPRS              | (410,711,7)      |                       | Gam.18 (TX power 0dBm)  | 104 / 105                                     | 121 / 122                                     | 130 / 130                                     | 980 <sub>TX</sub>        | mA   |  |

|                   | Transfer         | 850/900 MHz           | Gam.3 (TX power 33dBm)  | 378 / 385                                     | 398 / 408                                     | 410 / 419                                     | 1560 <sub>тх</sub>       | mA   |  |

|                   | Mode<br>class 10 |                       | Gam.17 (TX power 5dBm)  | 141 / 143                                     | 159 / 160                                     | 168 / 169                                     | 320 <sub>TX</sub>        | mA   |  |

|                   | (3Rx/2Tx)        | 1800/1900 MHz         | Gam.3 (TX power 30dBm)  | 267 / 279                                     | 286 / 301                                     | 297 / 313                                     | 1000 <sub>TX</sub>       | mA   |  |

|                   |                  |                       | Gam.18 (TX power 0dBm)  | 135 / 136                                     | 152 / 153                                     | 161 / 162                                     | 280 <sub>TX</sub>        | mA   |  |

TX means that the current peak is the RF transmission burst (Tx burst)

$_{\rm RX}$  means that the current peak is the RF reception burst (Rx burst)

\*N/A: That does not mean that no Open AT<sup>®</sup> application is possible in this specific mode. That means that the specific Dhrystone Open AT<sup>®</sup> application cannot allow this specific mode. (This is a worst case for the consumption measurement)

#

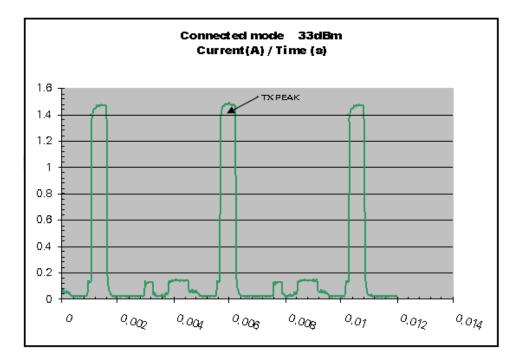

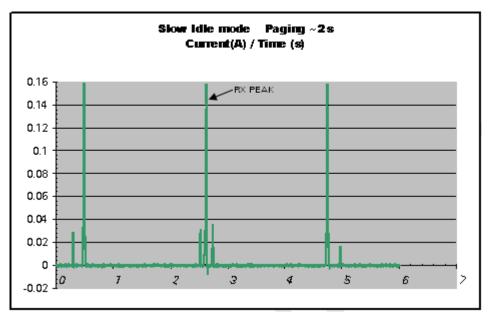

# 3.3.3 Consumption Waveform Samples

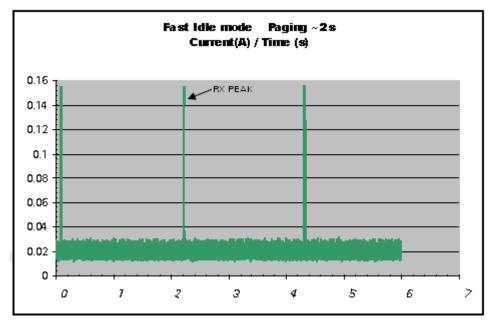

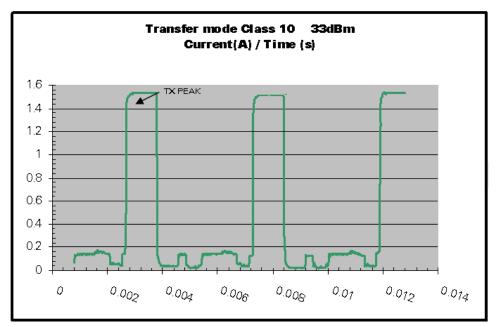

The consumption waveforms presented below are for an EGSM900 network configuration without the Open AT<sup>®</sup> Software Suite running on the Q64.

The usual VCC voltage is 3.6V.

Four significant operating mode consumption waveforms are described:

- Connected Mode (PCL5: Tx power 33dBm)

- Slow Idle mode (Paging 9)

- Fast idle mode (Paging 9)

- Transfer mode (GPRS class 10, gam.3: Tx power 33dBm )

The following waveform shows only the current curves.

#### **3.3.3.1 Connected Mode Current Waveform**

## WƏVECOM<sup>69</sup> © Confidential

Interfaces

#### 3.3.3.2 Slow Idle Mode Current Waveform

#### 3.3.3.3 Fast Idle Mode Current Waveform

## WƏVECOM<sup>©</sup> © Confidential

Interfaces

3.3.3.4 Transfer Mode Class 10 Current Waveform

## 3.3.4 Recommendations for Less Consumption

It is recommended to drive the GPIOs as indicated in the table below, especially when using the quiescent current.

| Signal | Pin<br>number | I/O | I/O type | Reset state | SW driver recommended |

|--------|---------------|-----|----------|-------------|-----------------------|

|        | number        |     |          |             | (output state)        |

| GPIO1  | 21            | I/O | 2V8-1    | Z           | 0 logic level         |

| GPIO2  | 22            | I/O | 2V8-1    | Undefined   | 0 logic level         |

| GPIO3  | 23            | I/O | 2V8-1    | Undefined   | 0 logic level         |

| GPIO4  | 24            | I/O | 2V8-1    | Z           | 0 logic level         |

| GPIO5  | 13            | I/O | 2V8-1    | Z           | 0 logic level         |

| GPIO6  | 33            | I/O | 2V8-1    | Z           | 0 logic level         |

| GPIO13 | 29            | I/O | Pull-up  | Pull-up*    | 0 logic level         |

| GPIO14 | 30            | I/O | Pull-up  | Pull-up*    | 0 logic level         |

| GPIO15 | 20            | I/O | 2V8-1    | Z           | 0 logic level         |

| GPIO16 | 35            | I/O | 2V8-1    | Z           | 0 logic level         |

\*GPI013 and GPI014 pull up are about 10K  $\Omega$ .

#

Page: 29 / 116

See chapter 3.4, "Electrical Information for Digital I/O" on page 30 for 2V8-1, 2V8-2, pull-up and open drain voltage characteristics and for Reset state definition.

If the LED is not necessary, it is possible to disable it.

For further details, refer to document [4] AT Command Interface Guide for Open  $AT^{\text{B}}$  Firmware v6.5.

# **3.4 Electrical Information for Digital I/O**

There are three types of digital I/O on the Q64: 2.8 volt CMOS type 1 (2V8-1), 2.8 volt CMOS type 2 (2V8-2) and Open drain.

The I/O concerned is all interfaces like GPIOs, PCM, etc.

The three types are described below:

#### Electrical characteristics of digital I/O

| 2.8 Volts type 1 (2V8-1 ) |                 |          |        |      |        |                          |  |  |

|---------------------------|-----------------|----------|--------|------|--------|--------------------------|--|--|

| Parameter                 |                 | I/O type | Minim. | Тур  | Maxim. | Condition                |  |  |

| Internal 2.8V powe        | er supply       | VCC_2V8  | 2.74V  | 2.8V | 2.86V  |                          |  |  |

| Input / Output pin        | V <sub>IL</sub> | CMOS     | -0.5V* |      | 0.84V  |                          |  |  |

|                           | V <sub>H</sub>  | CMOS     | 1.96V  |      | 3.2V*  |                          |  |  |

|                           | V <sub>oL</sub> | CMOS     |        |      | 0.4V   | $I_{OL} = -4 \text{ mA}$ |  |  |

|                           | V <sub>он</sub> | CMOS     | 2.4V   |      |        | I <sub>OH</sub> = 4 mA   |  |  |

|                           | I <sub>он</sub> |          |        |      | 4mA    |                          |  |  |

|                           | I <sub>oL</sub> |          |        |      | - 4mA  |                          |  |  |

\*Absolute maximum ratings

| 2.8 Volts type 2 (2V8-2 ) |                 |        |        |        |           |                          |  |

|---------------------------|-----------------|--------|--------|--------|-----------|--------------------------|--|

| Parameter                 | I/O type        | Minim. | Тур    | Maxim. | Condition |                          |  |

| Input / Output pin        | V <sub>IL</sub> | CMOS   | -0.3V* |        | 0.15V     |                          |  |

|                           | V <sub>IH</sub> | CMOS   | 1.6V   |        | 3.1V*     |                          |  |

|                           | V <sub>oL</sub> | CMOS   |        |        | 0.4V      | $I_{OL} = -4 \text{ mA}$ |  |

|                           | V <sub>он</sub> | CMOS   | 1.87V  |        |           | I <sub>OH</sub> = 4 mA   |  |

|                           | I <sub>он</sub> |        |        |        | 4mA       |                          |  |

|                           | I <sub>oL</sub> |        |        |        | - 4mA     |                          |  |

\*Absolute maximum ratings

WƏVECOM<sup>©</sup> © Confidential

| Open drain outputs type |                 |            |         |     |         |           |  |  |

|-------------------------|-----------------|------------|---------|-----|---------|-----------|--|--|

| Signal name             | Parameter       | I/O type   | Minimum | Тур | Maximum | Condition |  |  |

| BUZZER                  | V <sub>oL</sub> | Open Drain |         |     | 0.4V    |           |  |  |

|                         | I <sub>oL</sub> | Open Drain |         |     | 100mA   |           |  |  |

| Pull-up outputs type |                 |          |         |     |         |           |  |

|----------------------|-----------------|----------|---------|-----|---------|-----------|--|

| Signal name          | Parameter       | I/O type | Minimum | Тур | Maximum | Condition |  |

| SDA /                | V <sub>IH</sub> | Pull-up  | 2V      |     |         |           |  |

| GPIO13               | V <sub>IL</sub> | Pull-up  |         |     | 0.8V    |           |  |

| and                  | V <sub>oL</sub> | Pull-up  |         |     | 0.4V    |           |  |

| SCL /<br>GPIO14      | I <sub>oL</sub> | Pull-up  |         |     | 3mA     |           |  |

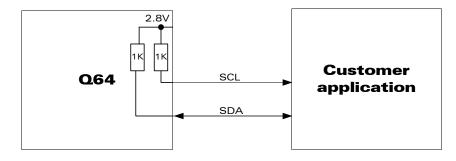

SDA and SCL are internally pulled up with each 1 k $\Omega$  resistor to voltage 2.8V (VREF) inside the Q64 Wireless CPU  $^{\rm 8}.$

The reset states for each I/O are given in the corresponding interface chapter descriptions. The state definitions are defined below:

|           | Reset state definition                                                                                                                                     |  |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Parameter | Definition                                                                                                                                                 |  |  |  |  |  |

| 0         | Set to GND                                                                                                                                                 |  |  |  |  |  |

| 1         | Set to supply 2V8                                                                                                                                          |  |  |  |  |  |

| Pull down | Internal pull down with ~60K resistor.                                                                                                                     |  |  |  |  |  |

| Pull up   | Internal pull up with ~60K resistor to supply 2V8.                                                                                                         |  |  |  |  |  |

| Z         | High impedance                                                                                                                                             |  |  |  |  |  |

| Undefined | Be careful, undefined should not be used in your application<br>if a special state is needed at reset. Those pins can be<br>toggling signals during reset. |  |  |  |  |  |

## WƏVECOM<sup>66</sup> © Confidential

# 3.5 I2C Bus

## 3.5.1 Features

The I2C interface includes a clock signal (SCL) and a data signal (SDA) complying with a 100Kbit/s-standard interface (standard mode: s-mode).

#### **3.5.1.1 Characteristics**

The I<sup>2</sup>C bus is always master.

The maximum speed transfer range is 400Kbit/s (Fast mode: f-mode).

For more information on the bus, see document [7] "I<sup>2</sup>C Bus Specification", Version 2.0, Philips Semiconductor 1998.

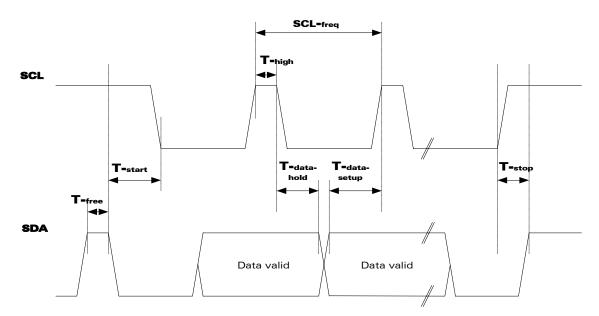

#### 3.5.1.2 I<sup>2</sup>C Waveforms

I<sup>2</sup>C bus waveform in master mode configuration:

Figure 3: I<sup>2</sup>C Timing diagrams, Master

####

| Signal       | Description                      | Minimum | Тур | Maximum | Unit |

|--------------|----------------------------------|---------|-----|---------|------|

| SCL-freq     | I <sup>2</sup> C clock frequency | 100     |     | 400     | KHz  |

| T-start      | Hold time START condition        | 0.6     |     |         | μs   |

| T-stop       | Setup time STOP condition        | 0.6     |     |         | μs   |

| T-free       | Bus free time, STOP to START     | 1.3     |     |         | μs   |

| T-high       | High period for clock            | 0.6     |     |         | μs   |

| T-data-hold  | Data hold time                   | 0       |     | 0.9     | μs   |

| T-data-setup | Data setup time                  | 100     |     |         | ns   |

## AC characteristics

## 3.5.2 Pin Description

| Signal | Pin<br>number | I/O | I/O type | Reset state | Description     | Multiplexed<br>with |

|--------|---------------|-----|----------|-------------|-----------------|---------------------|

| SDA    | 29            | I/O | Pull-up  | Pull-up*    | Serial Data     | GPIO13              |

| SCL    | 30            | 0   | Pull-up  | Pull-up*    | Serial<br>Clock | GPIO14              |

\*SDA and SCL pull-up are about 10K  $\Omega$

See chapter 3.4, "Electrical Information for Digital I/O" on page 30 for 2V8-1, 2V8-2, pull-up and open drain voltage characteristics and for Reset state definition.

The two lines are internally pulled up with each 1 K $\Omega$  resistor to voltage 2.8V (VREF) inside the Q64 Wireless CPU<sup>®</sup>.

# Figure 4: I<sup>2</sup>C bus configuration inside the Wireless CPU<sup>®</sup>

The I<sup>2</sup>C bus is compliant with the Standard mode (baud rate 100Kbit/s) and the Fast mode (baud rate 400Kbit/s).

#

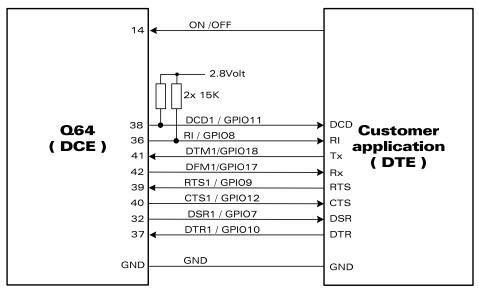

# 3.6 Main Serial Link (UART1)

A flexible 8-wire serial interface is available, compliant with V24 protocol signaling, but not with V28 (electrical interface) due to a 2.8 volts interface.

## 3.6.1 Features

The maximum baud rate of the UART1 is 921 Kbit/s.

The signals are as follows:

- TX data (DTM1)

- RX data (DFM1)

- Request To Send (RTS1)

- Clear To Send (CTS1)

- Data Terminal Ready (DTR1)

- Data Set Ready (DSR1)

- Data Carrier Detect (DCD1)

- Ring Indicator (RI).

| Signal | Pin<br>number         | I/O | l/O<br>type | Reset<br>state | Description             | Multiplexed<br>with |

|--------|-----------------------|-----|-------------|----------------|-------------------------|---------------------|

| DTM1*  | 41                    | I   | 2V8-1       | Z              | Transmit serial<br>data | GPIO18              |

| DFM1*  | 42                    | 0   | 2V8-1       | 1              | Receive serial<br>data  | GPIO17              |

| RTS1*  | 39                    | I   | 2V8-1       | Z              | Request To<br>Send      | GPIO9               |

| CTS1*  | 40                    | 0   | 2V8-1       | Z              | Clear To Send           | GPIO12              |

| DSR1*  | 32                    | 0   | 2V8-1       | Z              | Data Set Ready          | GPIO7               |

| DTR1*  | 37                    | I   | 2V8-1       | Z              | Data Terminal<br>Ready  | GPIO10              |

| DCD1*  | 38                    | 0   | 2V8-1       | Undefined      | Data Carrier<br>Detect  | GPIO11              |

| RI*    | 36                    | 0   | 2V8-1       | Undefined      | Ring Indicator          | GPIO8               |

| GND    | 2, 4, 6, 8,<br>10, 12 |     | GND         |                | Ground                  |                     |

## 3.6.2 Pin Description

See chapter 3.4, "Electrical Information for Digital I/O" on page 30 for 2V8-1, 2V8-2, pull-up and open drain voltage characteristics and for Reset state definition.

\*According to PC view

####

With the Open AT<sup>®</sup> Software Suite 1.0 / V2.0 when the UART1 service is run the multiplexed signals are unavailable for other purposes. Likewise, if one or more GPIOs (of this table) are allocated the UART1 service is unavailable.

The **rising time** and **falling time** of the reception signals (mainly DTM1) must be shorter than **300 ns**.

#### Recommendation:

The Q64 is designed to operate with all serial interface signals. It is mandatory to use RTS1 and CTS1 for hardware flow control in order to avoid data corruption during transmission.

#### 5-wire serial interface hardware design:

- Signal: DTM1\*, DFM1\*, RTS1\*, CTS1\*

- The signal DTR1\* must be managed following the V24 protocol signalling if we want to use the slow idle mode

- Please refer to the document [4] AT Command Interface Guide for Open AT<sup>®</sup> Firmware v6.5 for more information.

#### 4-wire serial interface hardware design:

- DTM1\*, DFM1\*, RTS1\*, CTS1\*

- The signal DTR1\* must be configured at the low level.

- Please refer to the document [4] AT Command Interface Guide for Open AT<sup>®</sup> Firmware v6.5 for more information.

#### 2-wire serial interface hardware design:

- It is possible for connected external chip but not recommended (and forbidden for AT command or modem use)

- The flow control mechanism must be managed by the customer.

- DTM1\*, DFM1\*

- The signal DTR1\* must be configured at the low level.

- The signals RTS1\*, CTS1\* are not used, please configure the AT command (AT+IFC=0,0 see document [4] AT Command Interface Guide for Open AT<sup>®</sup> Firmware v6.5).

- The signal RTS1\* must be configured at the low level.

- Please refer to the document [4] AT Command Interface Guide for Open AT<sup>®</sup> Firmware v6.5 for more information.

####

Interfaces

## 3.6.3 Application

The level shifter must be set at 2.8V compliant with a V28 electrical signal.

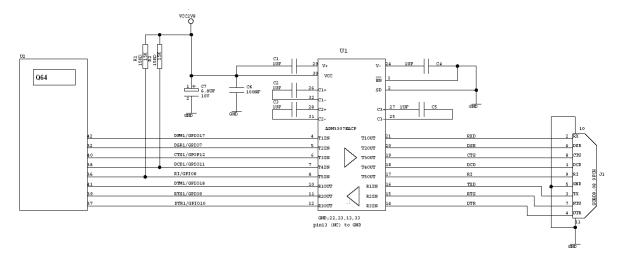

## Figure 5: Example of RS-232 level shifter implementation for UART1

U1 chip also protects the Q64 against ESD at 15KV. (Air Discharge).

#### Recommended components:

- R1, R2 : 15KΩ

- C1, C2, C3, C4, C5 : 1uF

- C6 : 100nF

- C7: 6.8uF TANTAL 10V CP32136 AVX

- U1 : ADM3307EACP ANALOG DEVICES

- J1 : SUB-D9 female

R1 and R2 are necessary only during Reset state to lift RI and DCD1 signals to high level.

The ADM3307EACP chip is able to reach **921Kb/s\***. If other level shifters are used, make sure that their speeds are compliant with the UART1 speed.

\*: For this baud rate, the power supply must be provided by an **external regulator at 3.0 V**.

The ADM3307EACP can be powered by an external regulator at 2.8 V (the baud rate will be limited up to 720kbps).

If the UART1 interface is connected directly to a host processor, it is not necessary to use level shifters. The interface can be connected as shown below:

####

## V24/CMOS possible design:

The design shown in the figure above is a basic design.

However, a more flexible design to access this serial link with all modem signals is shown below:

## Figure 7: Example of full modem V24/CMOS serial link implementation for UART1

It is recommended to add a  $15 \text{K}\Omega$  pull-up resistor on RI and DCD1 to set high level during reset state.

The UART1 interface is 2.8 volt type, but is 3 volt tolerant.

####

This document is the sole and exclusive property of WAVECOM. Not to be distributed or divulged without prior written agreement.

The Q64 UART1 is designed to operate with all serial interface signals. It is mandatory to use RTS1 and CTS1 for hardware flow control in order to avoid data corruption during transmission.

Warning: If you want to activate Power down mode (Wavecom 32K mode) in your Open AT<sup>®</sup> application, you need to connect the DTR1 to a GPIO. Please refer to the document [4] AT Command Interface Guide for Open AT® Firmware v6.5 (see the "Appendixes") for more information on Wavecom 32K mode activation using the Open AT<sup>®</sup> Software Suite.

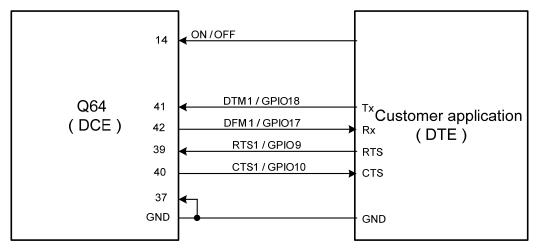

## **3.7 Auxiliary Serial Link (UART2)**

An auxiliary serial interface (UART2) is available on Q64. This interface may be used to connect a Bluetooth or a GPS chip controlled by an Open AT<sup>®</sup> Plug-in.

#### 3.7.1 Features

Maximum baud rate of the UART2 is 921 Kbit/s.

The signals are as follows:

- TX data (DTM3)

- RX data (DFM3)

#### 2-wire serial interface hardware design:

- DTM3\*, DFM3\*

- Please configure the AT command (AT+IFC=0,0) to start accessing UART2.

- Please refer to the document [4] AT Command Interface Guide for Open AT<sup>®</sup> Firmware v6.5.

| Signal | Pin<br>number         | I/O | I/O type | Reset<br>state | Description          |

|--------|-----------------------|-----|----------|----------------|----------------------|

| DTM3*  | 43                    | Ι   | 2V8-2    | Z              | Transmit serial data |

| DFM3*  | 44                    | 0   | 2V8-2    | Z              | Receive serial data  |

| GND*   | 2, 4, 6,<br>8, 10, 12 |     | GND      |                | Ground               |

#### 3.7.2 Pin Description

\* According to PC view

See chapter 3.4, "Electrical Information for Digital I/O" on page 30 for 2V8-1, 2V8-2, pull-up and open drain voltage characteristics and for Reset state definition.

#### WƏVECOM<sup>66</sup> © Confidential

## 3.7.3 Application

The voltage level shifter must be set at 2.8V and compliant with a V28 electrical signal.

## Recommended components:

Capacitors

- C1 : 220nF

- C2, C3, C4 : 1μF

Inductor

L1 : 10μH

RS-232 Transceiver

- U1 : LINEAR TECHNOLOGY LTC2802IDE

- J1 : SUB-D9 female

The LTC2802 can be powered by an external regulator at 2.8 V.

The UART2 interface can be connected directly to others components if the voltage interface is 2.8 V.

####

## **3.8 SIM Interface**

The Subscriber Identification Module can be directly connected to the Q64 through this dedicated interface.

#### 3.8.1 Features

The SIM interface controls the 1.8V and 3V SIM cards.

It is recommended to add Transient Voltage Suppressor diodes (TVS) on the signal connected to the SIM socket in order to prevent any Electrostatic Discharge.

TVS diodes with low capacitance (less than 10 pF) must be connected on SIMCLK and SIMDAT signals to avoid any disturbance during the rising and falling edges.

These types of diodes are mandatory for the Full Type Approval. They shall be placed close to the SIM socket.

The following references can be used: DALC208SC6 from ST Microelectronics.

5 signals exist:

- SIMVCC: SIM power supply.

- SIMRST: reset.

- SIMCLK: clock.

- SIMDAT: I/O port.

- SIMDET: SIM card detect.

The SIM interface controls a 3V / 1V8 SIM. This interface is fully compliant with GSM 11.11 recommendations concerning SIM functions.

####

| Parameter              | Conditions                 | Minim.     | Тур   | Maxim. | Unit |

|------------------------|----------------------------|------------|-------|--------|------|

|                        |                            |            | - 71- |        |      |